# tinyML. Summit

Miniature dreams can come true...

March 28-30, 2022 | San Francisco Bay Area

# Brains into sensors with Al in the Edge

Andrea Onetti Executive Vice President MEMS Sensors Sub-Group Analog, MEMS and Sensors Group

**STMicroelectronics**

# Is it a far-off future?

# The MEMS journey

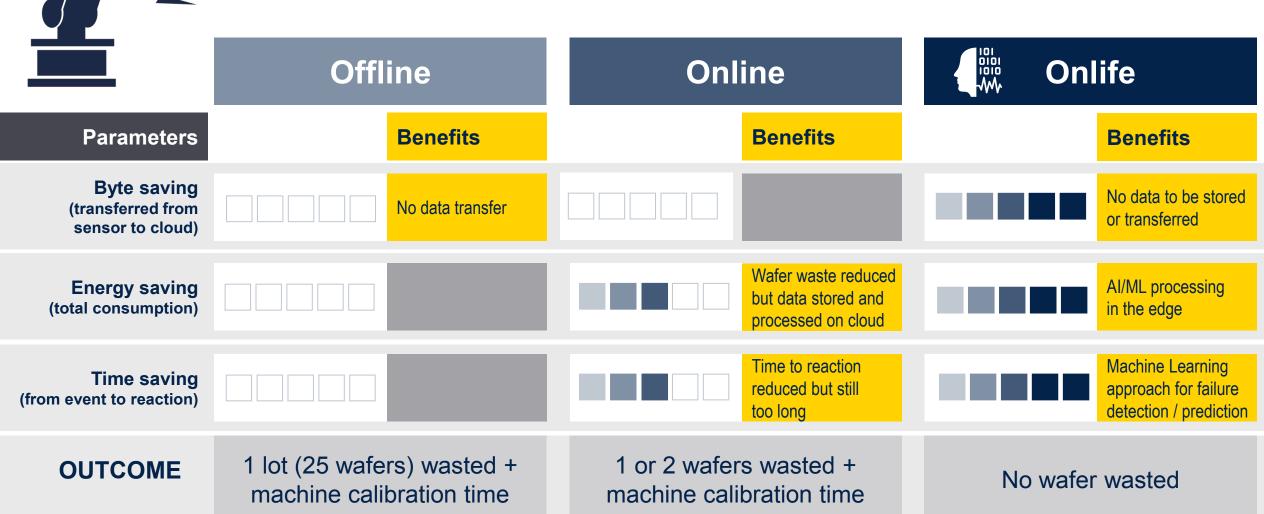

#### Offline era

#### Online era

2000

**2010**

A paradigm change in the man-machine interface

MEMS technology: from a concept to a product

**Sensor's proliferation and connections to Cloud**

Performance improvement and technology fusion

The fusion of technology and life

Standalone devices able to sense, process and take action

# Systems where sensors live: the evolution

Offline era

**Fragmented**

The simplest configuration: independent systems

**Online** era

Connected

Intertwined nodes enable efficient data exchange

Onlife era

**Trained**

Edge AI local decision making with maximum privacy

# Industry 5.0 challenges

# Sensor's semiconductors challenges for Edge Al

**OPTIMAL POWER (uW) PER PERFORMANCE CAPABILITIES** SUPER TINY SILICON LIMITED LOGIC AND MEMORY STORAGE **TECHNOLOGY ARCHITECTURE ECOSYSTEM COMPATIBILITY** ADVANCED TOOLS FOR INCREASED PRODUCTIVITY

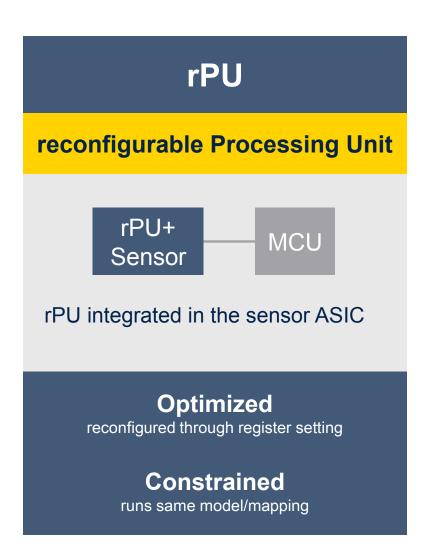

# Migrating intelligent processing From "on the Edge" to "in the Edge"

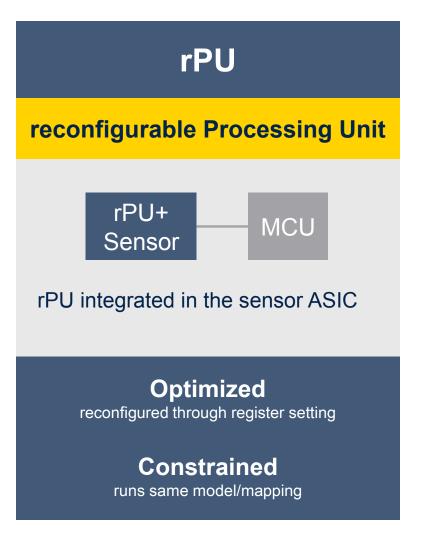

Sensor + MCU Microcontroller **MCU** Sensor MCU standalone or hosted in the sensor package **Standard** MCU runs the algorithms Runs any kind of SW provided it fits the MCU specs

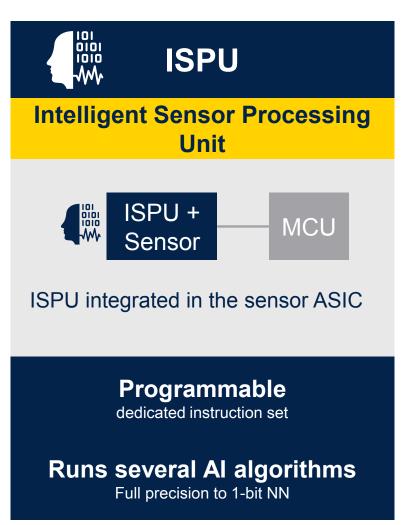

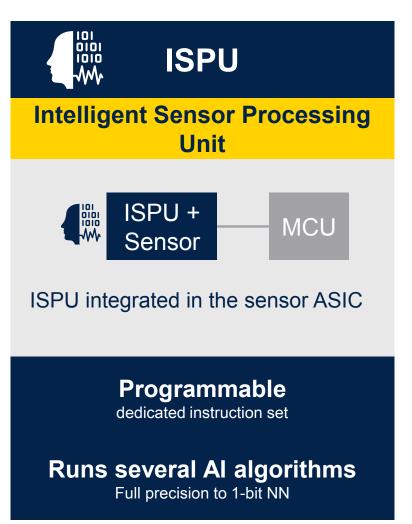

# ISPU: winning the challenges

#### **DSP for real-time processing and Artificial Intelligence**

#### **Small area**

down to 8 kgates

#### Standard package

3 x 2.5 x 0.83 mm

#### RAM based

40 kiloBytes (program + execution)

#### Full precision

Floating Point Unit

#### **Binary Neural Network**

convolution acceleration

#### **Optimization**

Power consumption vs. performance

# Optimization: power consumption vs performance

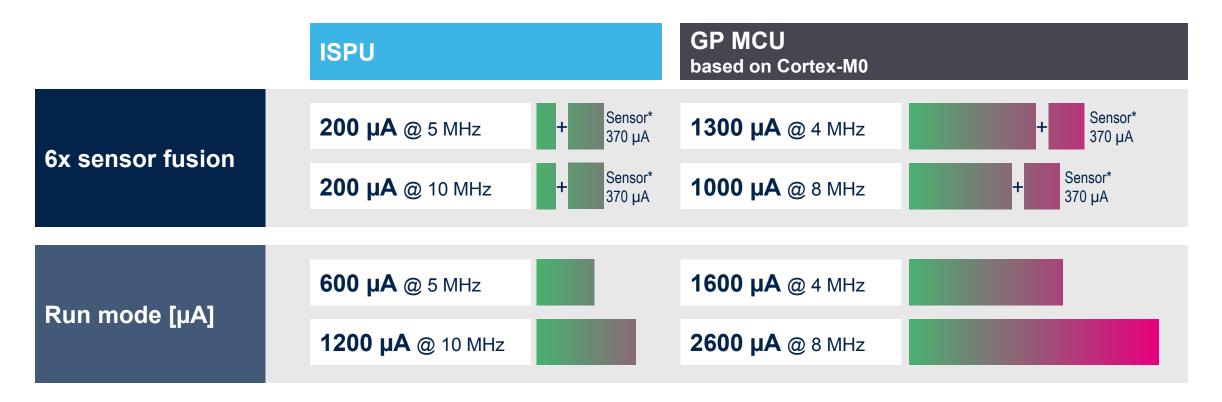

5x less current consumption for sensor fusion on ISPU than on M0 Below 600 μA for sensor fusion in the edge

# Binary Neural Network (BNN) on ISPU

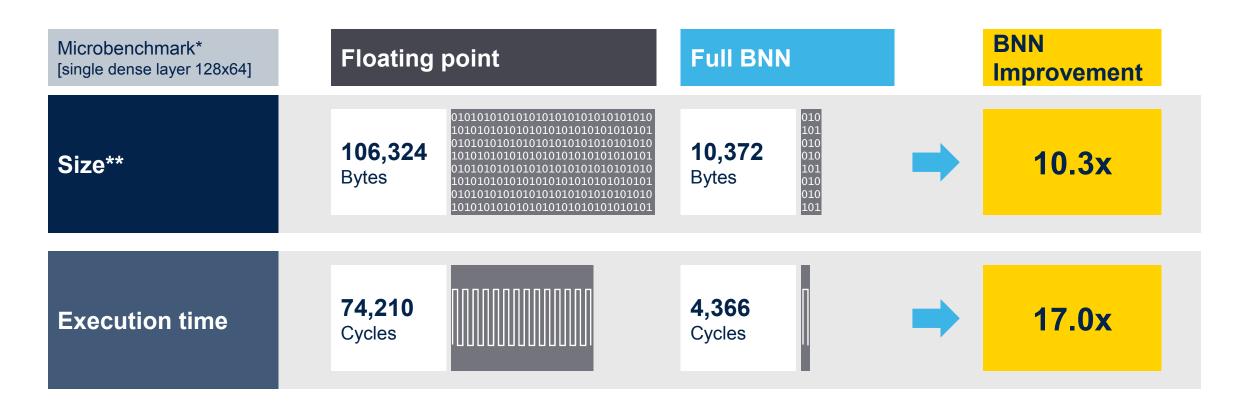

#### BNN on ISPU delivers over 10x better performance than floating point

life gugmented

<sup>\*</sup> Kernel size = 128 and number of kernels = 64. ISPU set at 5MHz frequency

<sup>\*\*</sup> Full Application size: data + code + internal buffers + system libs

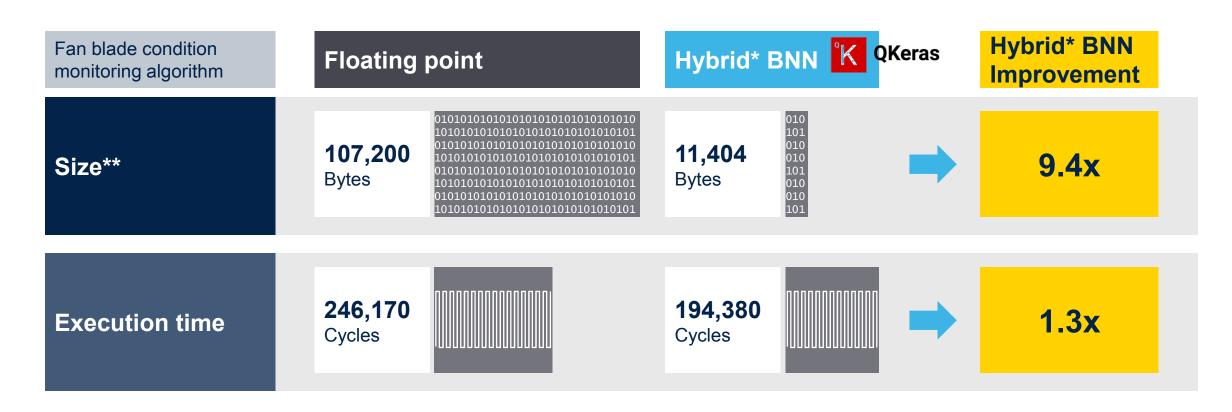

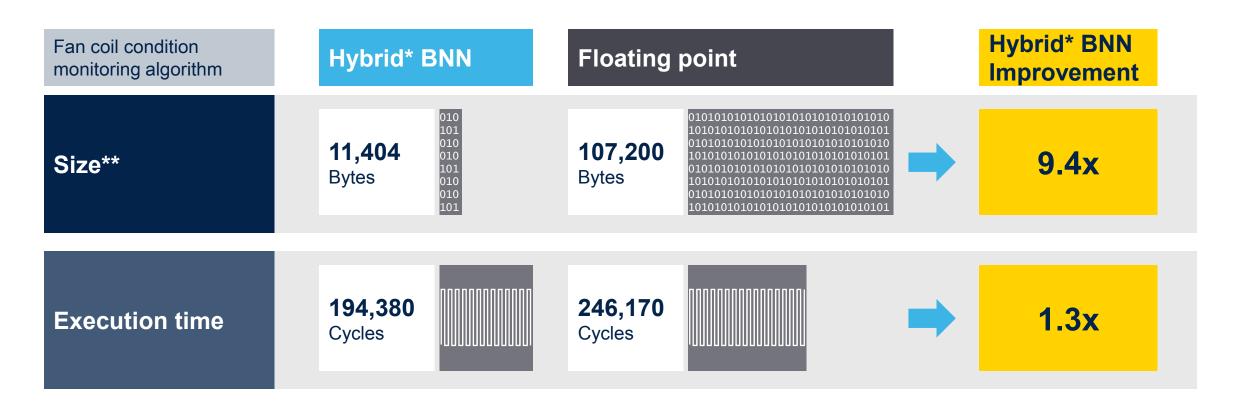

# Hybrid Binary Neural Network (BNN) on ISPU

#### ISPU makes solutions ready for Onlife with faster and smaller algos

<sup>\*</sup> Some layers are floating point activations with binary weights, some are fully binarized (weights and activations). ISPU set at 5MHz frequency

<sup>\*\*</sup> Full Application size: data + code + internal buffers + system libs

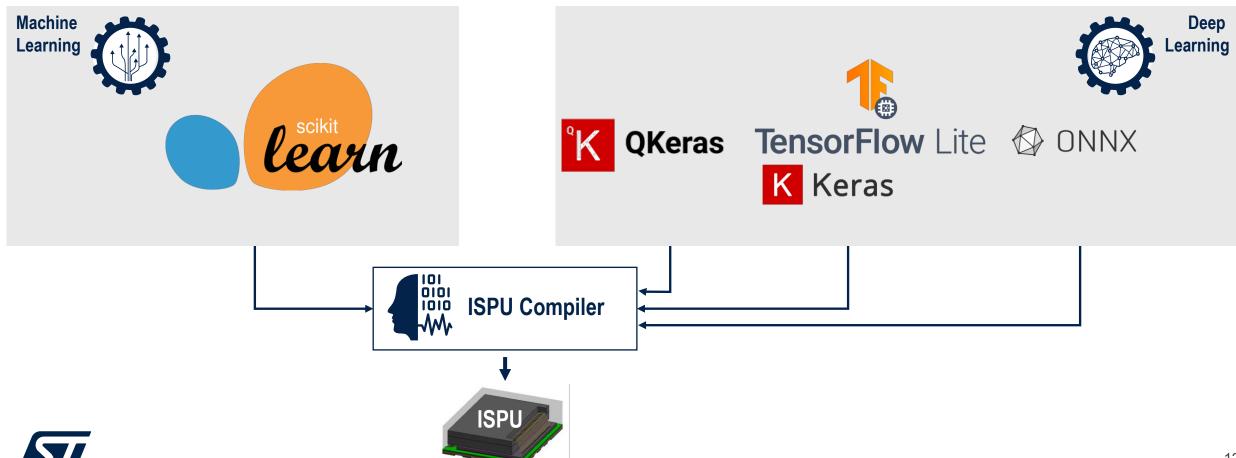

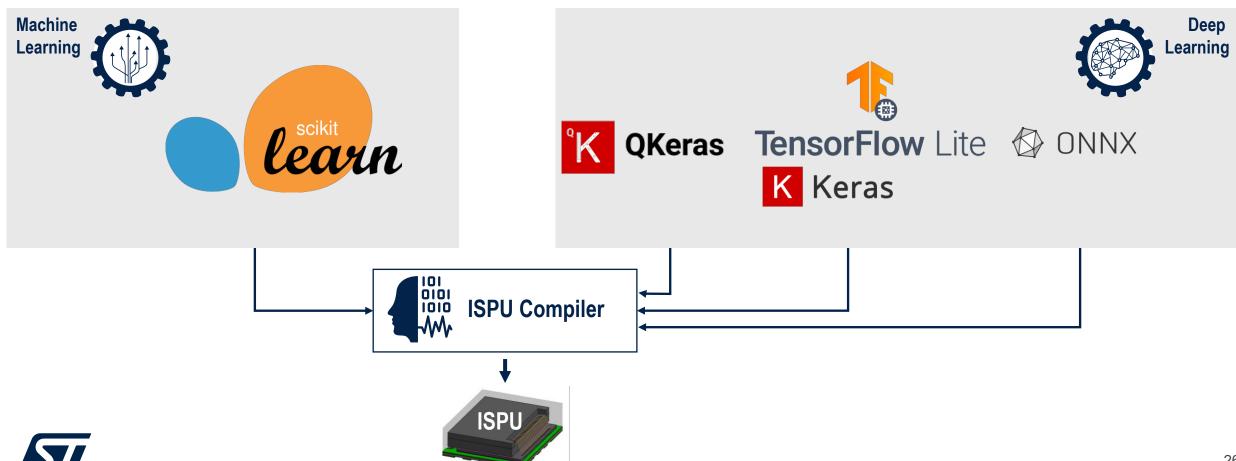

# In-sensor Machine Learning & Deep Learning

#### ST ISPU delivers more options and greater freedom

# ISPU in the Edge Al

Interoperates with

And?

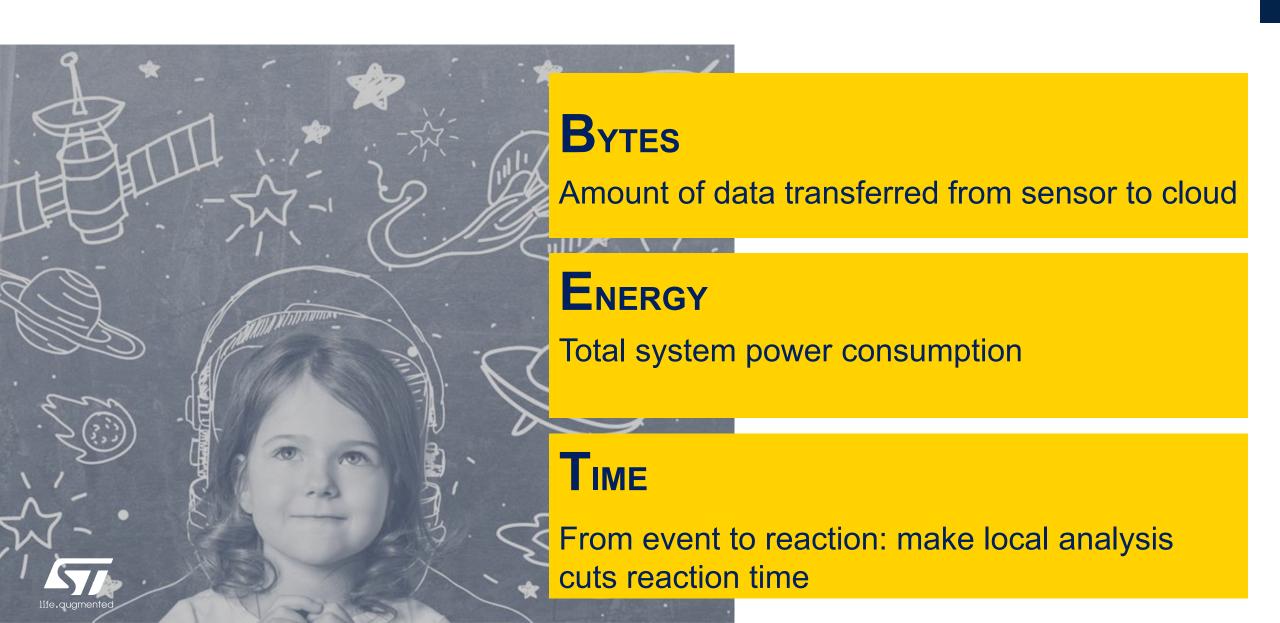

## The B.E.T. benchmark

# An example: the robotic arm handling

# "In" the Edge: towards a new ecosystem

## What's need to be explored together for ISPU?

Development of new benchmarks, and design tools to serve this innovation

Raise productivity and achieve synergies within the embedded developer community

## Takeaways

# Our technology starts with You

© STMicroelectronics - All rights reserved.

ST logo is a trademark or a registered trademark of STMicroelectronics International NV or its affiliates in the EU and/or other countries. For additional information about ST trademarks, please refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>.

All other product or service names are the property of their respective owners.

# Systems where sensors live

Offline era

**Fragmented**

**Online** era

Connected

Onlife era

**Trained**

# From "on the Edge" to "in the Edge"

Sensor + MCU **Microcontroller MCU** Sensor MCU standalone or hosted in the sensor package **Standard** MCU runs the algorithms Runs any kind of SW provided it fits the MCU specs

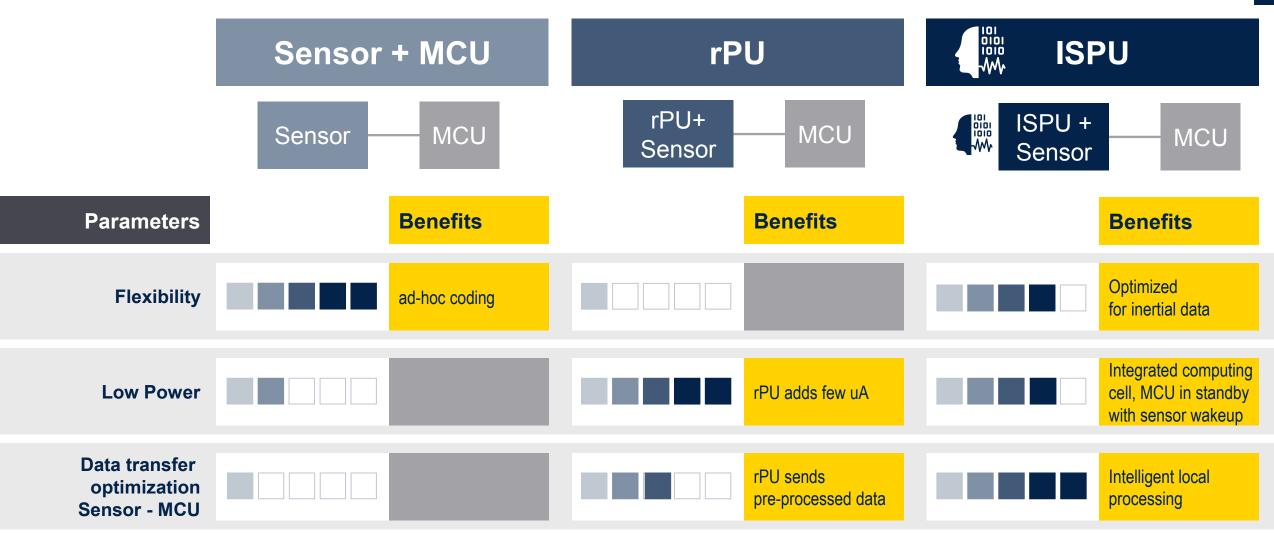

# One solution cannot fit all, but ISPU comes close

# The 3 design criteria for working in the Edge

#### Local

In the Edge: data privacy, low power...

#### **Fast**

Ad-hoc processor customization for real-time execution

#### Intelligent

Runs complex AI analyses and takes actions

## Sensor fusion on ISPU consumes far less current

5x less current consumption for sensor fusion on ISPU than on M0 Below 600 μA for sensor fusion in the edge

# Running Hybrid Binary Neural Network (BNN) for condition monitoring

#### ISPU makes solutions ready for Onlife with faster and smaller algos

<sup>\*</sup> Some layers are floating point activations with binary weights, some are fully binarized (weights and activations). ISPU set at 5MHz frequency

<sup>\*\*</sup> Full Application size: data + code + internal buffers + system libs

# BNN on ISPU far outperforms floating point

BNN on ISPU delivers over 10x better performance than floating point ISPU can now run dense SW layers in the Edge

Microbenchmark\*

[single dense layer 128x64]

Full BNN

Floating point

BNN Improvement

Size\*\*

**10,372**Bytes

**106,324** Bytes

10.3x

**Execution time**

**4,366** Cycles

**74,210** Cycles

17.0x

<sup>\*</sup> Kernel size = 128 and number of kernels = 64. ISPU set at 5MHz frequency

<sup>\*\*</sup> Full Application size: data + code + internal buffers + system libs

# In-sensor Machine Learning & Deep Learning

#### ST ISPU delivers more options and greater freedom

### ISPU - Toolkit

#### **Compilation Tool**

- Compiler (GNU) / Assembler (GNU) / Linker (GNU)

- Neural network library generation from high level tools (Keras, Tensorflow, etc.)

- Ad hoc optimization for ISPU target

#### **IDE Tools**

- Source-level debugger (GNU) / On-chip debugger

- Simulator (STMicroelectronics)

- Eclipse graphical interface

#### **Runtime**

- Platform SDK / Peripheral drivers

- Platform libraries

# ISPU with NanoEdge™ AI for self-learning solutions

Onlife-ready: classify data patterns and detect in the edge

Commercial libraries ready to deploy on ISPU

Reference design with customization and support

# Sensor's semiconductors challenges

**ADVANCED TOOLS FOR INCREASED PRODUCTIVITY**

**ECOSYSTEM COMPATIBILITY WITH AI TOOLS**

PROVEN TECHNOLOGY ARCHITECTURE IN SUPER TINY PACKAGE

LIMITED LOGIC AND MEMORY STORAGE FOR EDGE AI

**OPTIMAL POWER (uW) PER PERFORMANCE CAPABILITIES**

Al @ Edge

#### tinyML Summit 2022 Sponsors

Sony Semiconductor Solutions Corporation

# Copyright Notice

The presentation(s) in this publication comprise the proceedings of tinyML® Summit 2021. The content reflects the opinion of the authors and their respective companies. This version of the presentation may differ from the version that was presented at the tinyML Summit. The inclusion of presentations in this publication does not constitute an endorsement by tinyML Foundation or the sponsors.

There is no copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies and may contain copyrighted material. As such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

tinyML is a registered trademark of the tinyML Foundation.

www.tinyML.org